# PAL Conversion Guide With Xilinx EPLD Data Sheets

August 1993

# Xilinx EPLDs The Best Solution for PAL® Conversion

# Welcome and thanks for your interest in Xilinx EPLD products.

If you're like most PAL designers, you're interested in converting your designs to more complex devices like Xilinx XC7200/A and XC7300 EPLDs. But you're probably also a bit skeptical about the different claims vendors have made about their products. The PAL Conversion Guide will help you better understand how PAL conversion is accomplished with Xilinx EPLD products.

# PAL conversion vs. PAL integration.

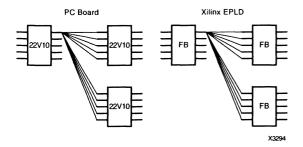

The typical design requirement is PAL conversion, but most products on the market today address PAL integration. The semantics here are very important. Any high pin-count logic device can *integrate* multiple PALs into a single device. But complex programmable logic devices, like FPGAs, differ architecturally from the simple array structures of PALs. This means that PAL integration works only after a lot of time and effort is spent in redesign. Even complex product term-based products can pose significant barriers to the integration process.

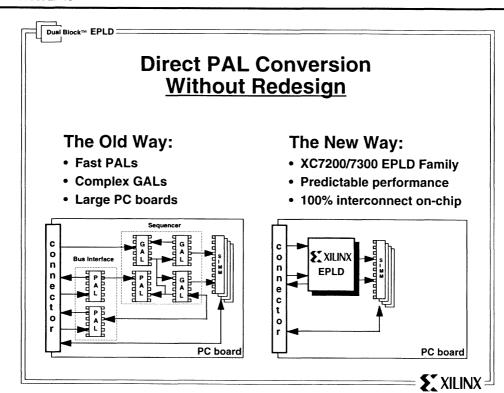

## Xilinx offers the first true PAL conversion process.

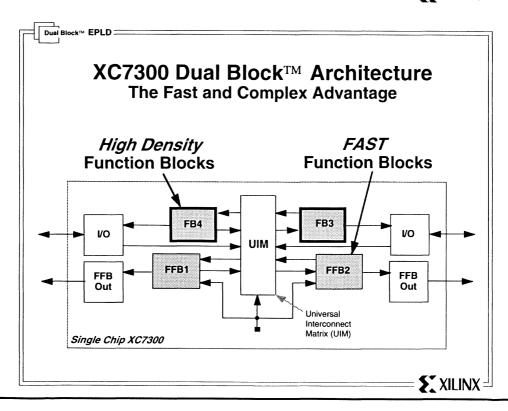

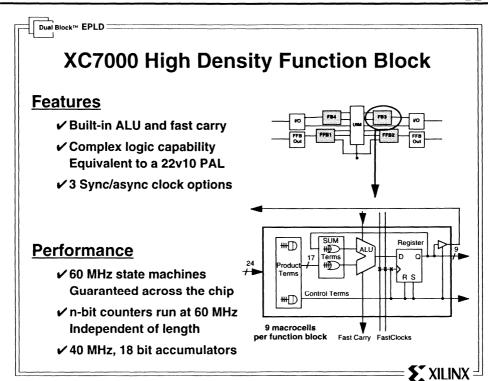

The Xilinx PAL conversion process allows you to take the original source files for your PAL or GAL based design, and directly convert it to either XC7200/A or XC7300 EPLDs, without redesign. Designs can be converted quickly and easily, with virtually no risk. If you use ABEL™, PALASM™ or CUPL™, it's no problem. You can easily convert designs done with these tools to a working XC7200/A or XC7300 device. The XC7300 family's unique Dual Block™ architecture, along with the PAL conversion utilities contained in the Xilinx EPLD software, make it easy.

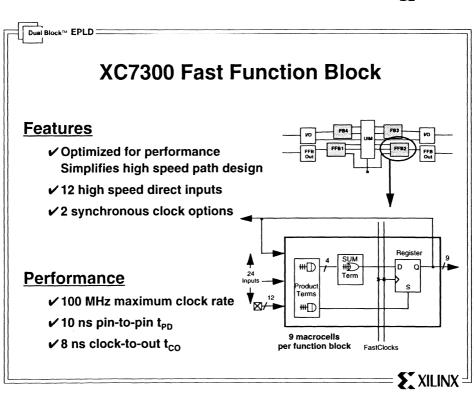

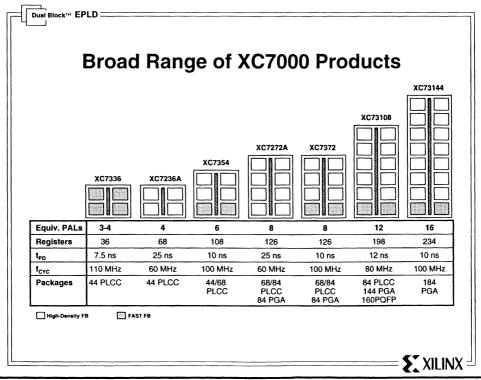

The Dual Block architecture incorporates two types of logic blocks on each device. One type is optimized for simple PAL functions that require high pin-to-pin speed, and the other type is optimized for product-term-rich PAL or GAL functions that require high clock cycle rates. Unlike other CPLDs, Xilinx devices are FAST and COMPLEX. This allows individual PAL devices to be mapped directly to the appropriate logic, and connected just as they appear on the PCB.

Please take a few minutes to look over the Xilinx PAL Conversion Guide. We believe you'll agree that Xilinx EPLDs provide *the best solution for PAL conversion*.

**EPLD Product Marketing**

Xilinx, the Xilinx logo, and XACT are registered trademarks of Xilinx, Inc. All XC-prefix product designations, Dual-block, XEPLD, UIM, Logic Cell, and LCA are trademarks of Xilinx, Inc. The Programmable Gate Array Company is a Service Mark of Xilinx Inc. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. ABEL is a trademark of DATA I/O Corporation. CUPL is a trademark of Logical Devices, Inc. All other trademarks are property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patents, copyrights or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, will not assume responsibility for the use of any circuitry described other than circuitry entirely embodied in its products. Manufactured under one or more of the following U. S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,783,607; 4,820,937; 4,821,233; 4,835,418; 4,847,612; 4,853,626; 4,855,619; 4,855,669; 4,870,302; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858. Xilinx cannot assume responsibility for any circuits shown or represent that they are free from patent infringement or of any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

©1993 Xilinx, Inc. All rights reserved.

# **SECTION TITLES**

|   | AILIINA                  | SECTION TITLES   |

|---|--------------------------|------------------|

| 1 | Xilinx EPLD Products     |                  |

| 2 | Direct PAL Conversion Us | ing Xilinx EPLDs |

| 3 | XC7200/A EPLD Family     |                  |

| 4 | XC7300 EPLD Famly        |                  |

| 5 | Packages                 |                  |

| 6 | Applications             |                  |

| 7 | Sales Offices            |                  |

|   |                          |                  |

# 1 Xilinx EPLD Products

- 2 Direct PAL Conversion Using Xilinx EPLDs

- 3 XC7200/A EPLD Family

- 4 XC7300 EPLD Family

- 5 Packages

- 6 Applications

- 7 Sales Offices

| - |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

# **XC7000 Product Lines**

New, Enhanced

XILINX

EPLD Products

The BEST Solution for PAL Conversions

# **SECTION 2**

1 Xilinx EPLD Products

# 2 Direct PAL Conversion Using Xilinx EPLDs

- 3 XC7200/A EPLD Family

- 4 XC7300 EPLD Family

- 5 Pagkages

- 6 Applications

- 7 Sales Offices

# Direct PAL Conversion Using Xilinx EPLDs

| Introduction               | 2-1 |

|----------------------------|-----|

| Xilinx EPLD Architecture   | 2-1 |

| Xilinx EPLD Software       | 2-3 |

| The PAL Conversion Process | 2-3 |

| Conclusion                 | 2-8 |

# Direct PAL Conversion Using Xilinx EPLDs

BY JEFFREY GOLDBERG

# Introduction

In order to remain competitive in the marketplace, companies are being driven to reduce product manufacturing costs while adding more features and improving reliability. Users of low density discrete PALs are turning to higher density erasable programmable logic devices (EPLDs) to meet these goals.

PALs are easy devices to use. Device timing is fixed, routing issues are nonexistent and the device architectures are simple and understandable. Many EPLDs however, exhibit timing unpredictability, routing limitations, and limited functionality that can trap the unwary first-time EPLD user. Couple that with the task of learning how to use new design-entry software, and what appeared to be a simple task can turn into a nightmare.

This application note shows how Xilinx EPLDs can be used to simplify the task of reducing the number of discrete low density PALs on a board. This direct PAL conversion is made possible by a unique combination of :

- Architectural features

- Software methodology

- Broad product family

# Xilinx EPLD Architecture

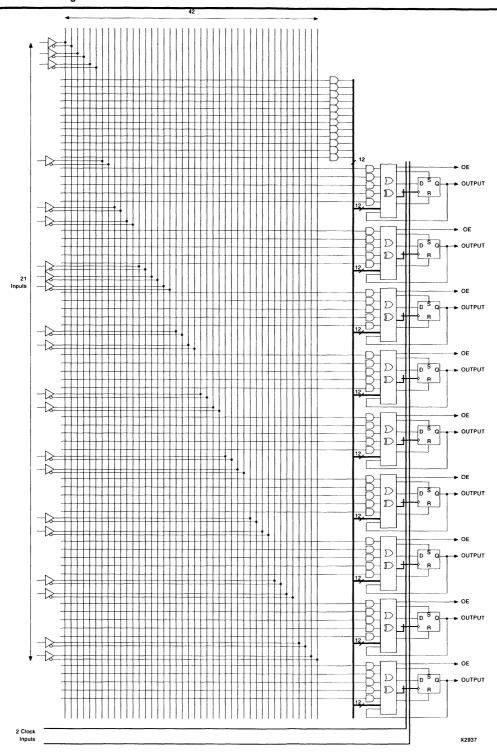

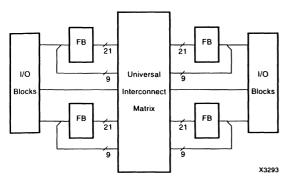

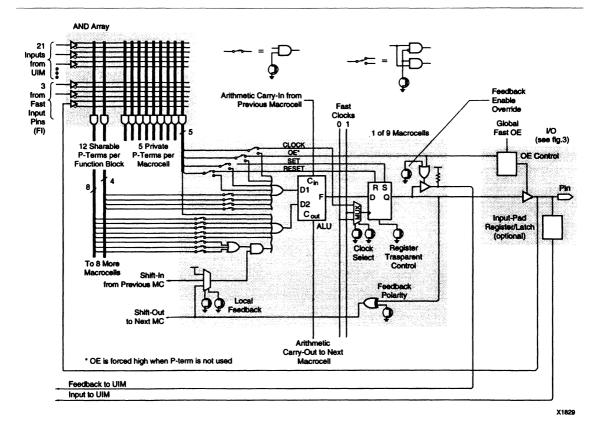

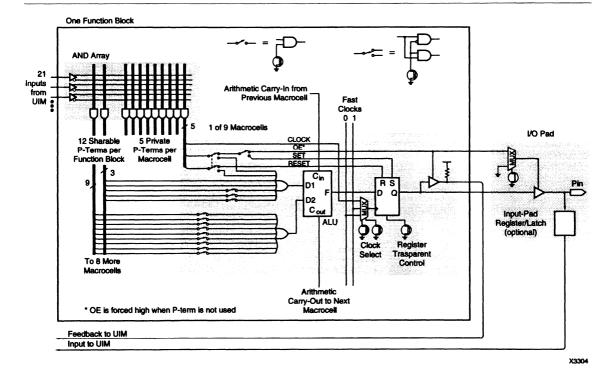

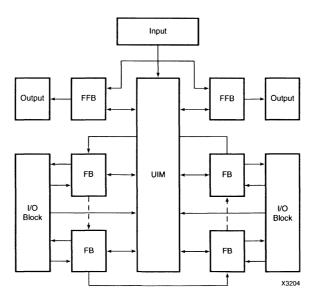

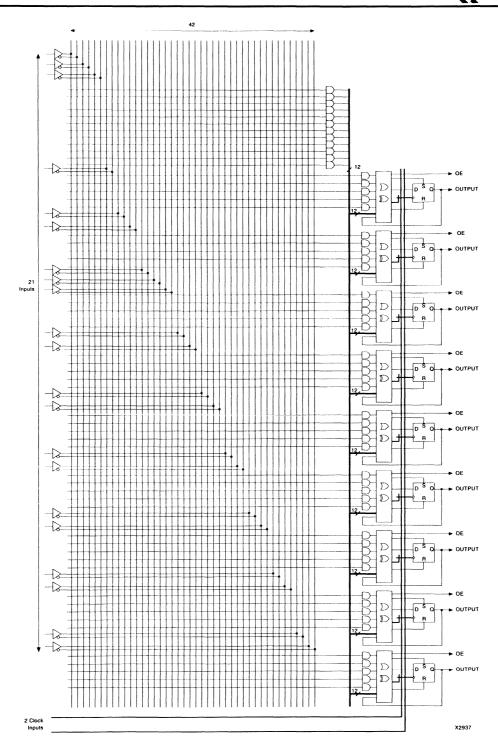

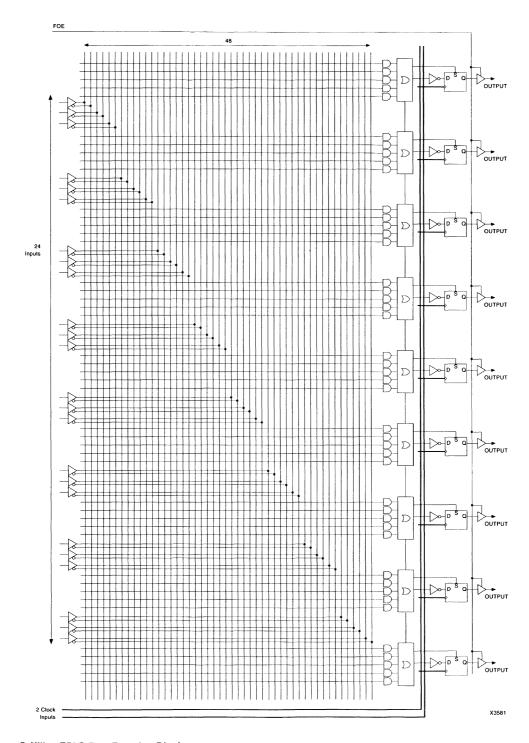

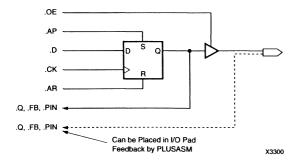

In order to support direct PAL conversion, Xilinx EPLDs have a PAL-like architecture. Each device consists of several PAL-like logic blocks, called Function Blocks (FBs), on a single IC, all interconnected by a fully populated switch matrix. Each FB can be thought of as a 21V9 PAL, with 21 complementary inputs and an AND-OR array with 57 product terms feeding 9 outputs.

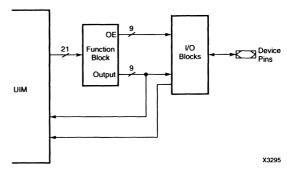

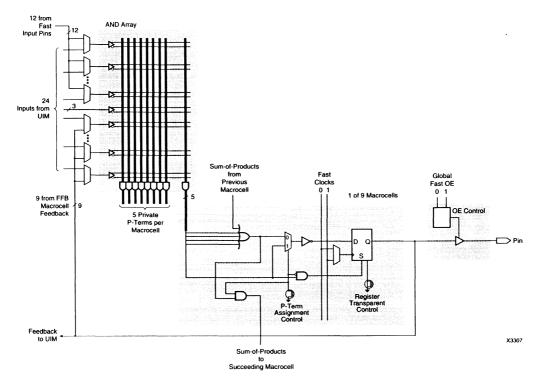

The Xilinx EPLD Function Block is highly flexible superset of the low density PAL. The product term intensive FB has five individual product terms per output. In addition, there are 12 product terms that are shared between all 9 outputs. Each output can be configured as either registered or combinatorial. Each register has individual set, reset and output enable control and can be clocked either individually or by global clocks. In addition, each output has an available XOR gate that can be used for XOR functions or toggle flip flop emulation.

Although product-term-intensive, the timing is fixed. No matter whether the output is performing a single product-term function or a 17 product-term function with the XOR gate, the timing doesn't change. Just like a PAL.

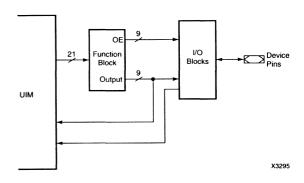

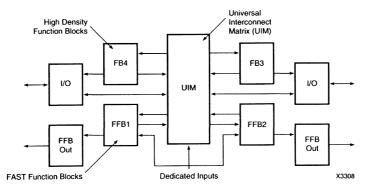

All of the Function Blocks on a Xilinx EPLD are interconnected by a fully populated Universal Interconnect Matrix  $(UIM^{\sim})$ .

Unlike other vendor's sparsely populated matrices that create routing problems and have fanout-dependent timing, the UIM is a fully populated, non-blocking switch matrix that features a constant delay, independent of fanout. Every Function Block output and every signal from every input and I/O pin all feed into the UIM. The UIM in turn drives every input of every FB. This means that each Function Block input can be driven by any input pin, any I/O pin and any Function Block output – just like connecting PALs on a board, but better.

In addition to serving as an interconnect, the UIM may also function as very wide input AND array. This allows the EPLD to generate product terms in the UIM – just like a low density PAL AND array. And like a PAL, propagation delay is fixed regardless of the number of signals used to generate the product term, or the source and destination of those signals.

Figure 1. Xilinx EPLD PAL-Like Function Block

Figure 2. Universal Interconnect Matrix

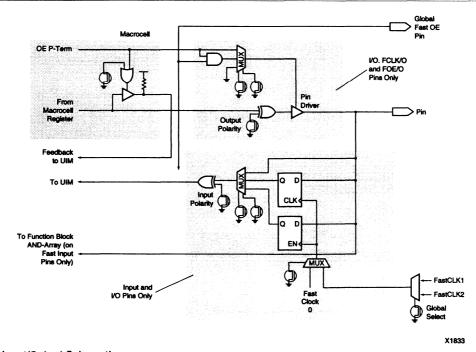

The EPLD has programmable I/O blocks for driving the device pins. The I/O blocks can be used to decouple the Function Block's outputs from the device pins so the Function Block outputs may be buried while still retaining the use of the pin as a device input. The I/O blocks also provide output inversion control and the ability to latch and register input signals.

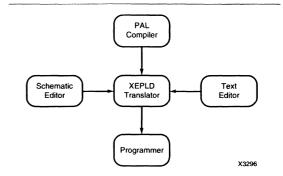

# Xilinx EPLD Software

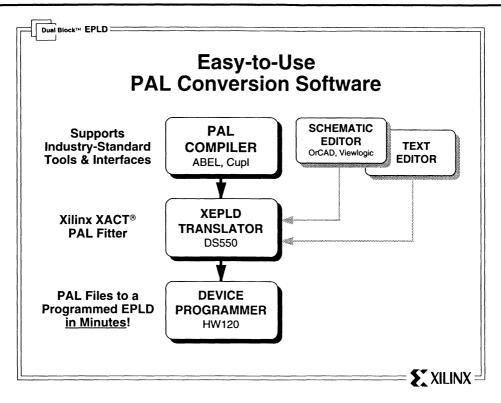

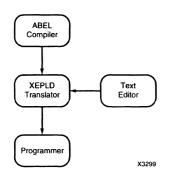

When it comes to programmable logic, silicon is only part of the solution. Software is required to translate ideas into reality. The Xilinx EPLD Translator (XEPLD™) works with industry standard PAL logic compilers and languages such as ABEL, CUPL and PALASM. One can directly import JEDEC files from old, proven designs using 22V10s and 20V8s.

The bottom line - the XEPLD system allows design entry with familiar front end tools. Once the design is entered, XEPLD simply acts as a fitter, taking the design description and mapping it into the chosen Xilinx EPLD.

In addition to being easy to use, XEPLD is very powerful. One of the most important functions of a fitter for high density programmable logic is Automatic Partitioning. The design can be entered without having to first partition it into Function Block-size pieces. This lets the designer concen-

Figure 3. The 100% Interconnect

Figure 4. I/O Block

trate on the functionality of the design, not its physical implementation.

### The PAL Conversion Process

The PAL conversion process is begun by identifying which group of PALs are to be converted to a single EPLD. Then choose the appropriate Xilinx EPLD, based on the I/O and logic requirements. Xilinx makes this process easier by offering each device in a variety of footprint-compatible packages. This flexibility allows the designer to upgrade to a higher density device without having to change the board layout, should the logic requirements change.

Since the timing of the Xilinx EPLD is absolutely predictable, it is an easy matter to verify that the design will meet all critical timing requirements. By eliminating delays getting on and off chip, even D series PALs can be converted to a single Xilinx EPLD.

The choice of whether to do equation-based design entry or schematic-based design entry is based primarily on the user's preference. Equation-based entry allows the user to concatenate PALASM equations from multiple PAL files without any restrictions on the PAL type. Equation-based entry gives the user more control over how the logic is mapped into the EPLD.

Figure 5. Development System Overview

Figure 6. XEPLD Runs Under the Xilinx Design Manager

On the other hand, schematic-based design entry may be easier to conceptualize, and it allows the user to directly import JEDEC files for 22V10 and 20V8 PALs (PALASM equations may be used for other PAL types).

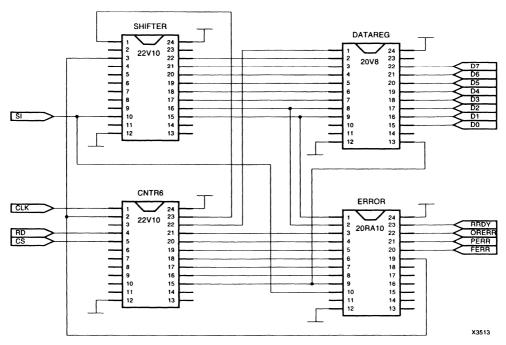

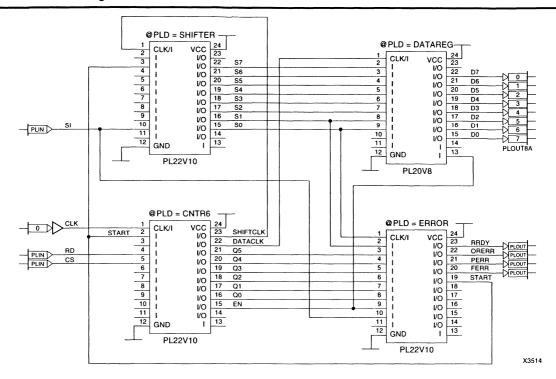

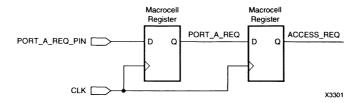

The following examples show how to use XEPLD to directly convert a multiple-PAL design to a single Xilinx EPLD. The examples show the use of both equation and schematic-based design entry methods. The design, shown in Figure 7, implements a UART originally implemented with two 22V10s, a 20V8 and a single 20RA10.

Direct PAL conversion implies that there is absolutely no redesign necessary to convert the design to a single Xilinx EPLD. The reader, therefore, needs to be aware of two issues that may affect a design's suitability for direct conversion.

- Designs implemented with XOR PALs such as the 20X10A series require minor syntax changes in their PALASM output files to conform to how XOR operations are expressed for Xilinx EPLDs.

- Because asynchronous presets and resets function differently in different PALs, the architectures of the original PAL and the Xilinx EPLD need to be considered when converting the design. In the Xilinx EPLD architecture, inversions are performed before the register, not after the register output. If the original PAL performed the inversion after the register, (e.g. a 20RA10), its output pin goes HIGH when the register is reset,

whereas the Xilinx EPLD Function Block output would go LOW. A simple modification to the PAL's source code before generating the PALASM file may be all that is required (e.g. changing the reset to a preset).

# **Equation-Based Design Entry**

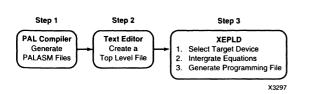

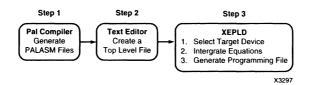

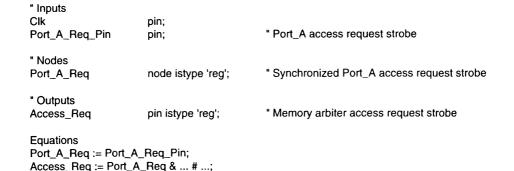

Direct PAL conversion is easily accomplished with a modular design approach. Each PAL in the design can be treated as an individual module. A top level design file simply links all of the modules together. Since this file need only contain declaration statements that manage the design (e.g. define the chip's inputs and outputs), it is created with a minimum of effort. XEPLD reads the top level file, concatenates the equations for each individual PAL, automatically partitions the equations and converts the multiple-PAL design to a single chip solution. This design flow is illustrated in Figure 8.

For each PAL in the design, generate a PALASM Boolean equation file from the original PAL source code. This is easily done with the ABEL XFER utility or the CUPL -c compiler option. At this time, verify that the signal names in each PAL pinlist establishes the proper signal connectivity for the design.

Using a text editor, write the top level design file. The design file PAL\_UART.PLD, shown in Figure 9, was created for the UART design. This file is written in PLUSASM, the XEPLD native syntax, and should look very familiar to those familiar with PALASM.

Figure 7. Original UART Design

Like PALASM, this file begins with a title block for design documentation, followed by INCLUDE\_EQN keywords that instruct XEPLD to concatenate the PALASM equations contained in each of the included files that were generated by the PAL compiler.

The CHIP statement contains the filename of the top level file (without the file extension) and targets a Xilinx EPLD.

INPUTPIN, OUTPUTPIN and NODE keywords then follow to define the devices inputs, outputs and nodes. This is followed by the FASTCLOCK keyword that assigns signals to the global FastClock lines.

Figure 8. Equation-Based Design Flow

The EQUATIONS keyword indicates where the equations section of the design file begins. After reading this keyword, XEPLD reads all of the equations in the included files.

After completing the top level design file, do the following:

· Select the target device:

Open up the FAMILY menu and select the XC7000 device family. Then open up the PART menu and select the target Xilinx EPLD.

• Integrate the equations:

Open up the FITTER menu and select FITEQN, then PAL\_UART.PLD. XEPLD then processes the design to create the database file PAL\_UART.VMH.

Generate the device programming file:

Open up the VERIFY menu and select MAKEPRG, then PAL\_UART.VMH. Assign the signature, PALUART.A, and XEPLD will now produce the device programming file. PAL UART.PRG.

The device can now be programmed and the correct system operation verified.

TITLE TOP LEVEL DESIGN FILE FOR PAL\_UART

AUTHOR EPLD APPLICATIONS

COMPANY XILINX DATE 2/3/93

INCLUDE\_EQN 'SHIFTER.PDS'

INCLUDE\_EQN 'CNTR6.PDS'

INCLUDE\_EQN 'DATAREG.PDS'

INCLUDE\_EQN 'ERROR.PDS'

CHIP PAL\_UART XEPLD

INPUTPIN SI RD CS

OUTPUTPIN D0 D1 D2 D3 D4 D5 D6 D7 RRDY ORERR PERR FERR

NODE S0 S1 S2 S3 S4 S5 S6 S7 EN Q0 Q1 Q2 Q3 Q4 Q5 DATACLK SHIFTCLK

PAR START

FASTCLOCK CLK

**EQUATIONS**

Figure 9. Top-Level Design File

## **Schematic-Based Design Entry**

The schematic design entry flow is also simple and straightforward. The XEPLD component library contains 22V10 and 20V8 PALs to simplify the PAL conversion process. It is a simple matter to connect the PALs exactly as in the original design and import JEDEC files that

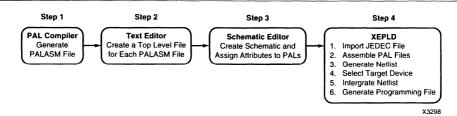

describe their functionality. For other PAL types such as the 20RA10 used in the original design, PALASM equation files can be used instead. XEPLD then processes the netlist and PAL files to convert the design to a single chip solution. This design flow is illustrated in Figure 10.

Figure 10. Schematic-Based Design Flow

For each 22V10 and 20V8 in the original design, use the existing JEDEC files generated by the PAL compiler. For other PAL types, generate a PALASM Boolean equation file. Then, using a text editor, create a top level file for each PAL that a PALASM equation file was created for. This file is similar to the top level design file for the equation based design entry, with two differences:

- The CHIP statement targets the PAL in the schematic, not a Xilinx EPLD

- A pinlist is used to define the pinout of the PAL in the schematic

Any PAL in the XEPLD component library that meets the I/O requirement can serve as the target device, but the PL22V10, PL20V8 and PLFPLA48 are recommended to take advantage of the automatic partitioner.

In this design example, a PL22V10 was chosen as the target device for the ERROR PAL, even though a 20RA10 was used in the original design. This is permitted because both the PL22V10 and PL20V8 library components have the full functionality of the Xilinx EPLD architecture and do not suffer the architectural limitations of the discrete devices they replace. The top level file, ERROR.PLD is shown in Figure 11. Note that each pin position must have either a signal name or a no-connect (NC) assigned to it.

Now use the schematic editor to capture the design. Assign an attribute to each PAL in the schematic that links the PAL to an intermediate file that describes it's function. In Viewlogic, the attribute @PLD=<file\_name> is assigned with the ViewDraw attribute command. When using OrCAD, edit the PAL's partfield to read PLPLD=<file\_name>. Save the design file when done.

TITLE

TOP LEVEL DESIGN FILE FOR ERROR DETECTOR PAL IN PAL\_UART DESIGN

AUTHOR

**EPLD APPLICATIONS**

COMPANY

XILINX

DATE

2/3/93

INCLUDE\_EQN

'ERROR.PDS'

CHIP

ERROR PL22V10

; 1 2 3 4 5 6 7 8 9 10 11 12

S0 S1 Q5 Q4 Q3 Q2 Q1 Q0 EN SI NC GND

13 14 15 16 17 18 19 20 21 22 23 24

NC NC NC NC NC PAR START FERR PERR OREER RRDY VCC

# **EQUATIONS**

Figure 11. PLUSASM File ERROR.PLD

Figure 12. PAL\_UART Workview Schematic

Now the design is ready to be processed.

# Generate the netlist:

Open up the TRANSLATE menu and select WIR2NET, then PAL\_UART.1 to generate a Viewlogic netlist. If the design was captured with OrCAD, select STD2NET instead, then PAL\_UART.SCH to generate the OrCAD netlist.

# Import a JEDEC file or Assemble the Equation File for each PAL in the schematic:

· To Import a JEDEC File:

Open up the TRANSLATE menu and select JED2PLD, then SHIFTER.JED to import the JEDEC file. Type in the desired filename for the equation file that will describe the PAL's functionality, SHIFTER.PLD, then select the PAL type, PL22V10. XEPLD will automatically partition the logic into one or more Function Blocks and create the intermediate PAL description file SHIFTER.VMH. Repeat this procedure for each JEDEC file to be imported.

To Assemble an Equation File:

Open up the TRANSLATE menu and select PLUSASM, then ERROR.PLD to assemble the top level file for the PAL. Remember, XEPLD will reference the equations in the included PALASM file, ERROR.PDS. XEPLD will

partition the logic and create the intermediate PAL description file ERROR.VMH.

## Integrate the netlist:

Open up the FITTER menu and select FITNET, then PAL\_UART.NET to integrate the netlist.

Generate the device programming file:

Open up the VERIFY menu and select MAKEPRG, then PAL\_UART.VMH. Assign the signature, PALUART.A, and XEPLD will now produce the device programming file, PAL\_UART.PRG.

The device can now be programmed, installed on the board and correct system operation verified.

### Conclusion

This application note demonstrates how easy it is to directly convert PAL based designs to a single Xilinx EPLD without any redesign. This direct conversion process is only possible when the target device logic blocks have a PAL-like architecture, the interconnect matrix is fully populated and chip timing is completely independent of product term utilization and layout. The Xilinx EPLD Translator simplifies this task by interfacing directly to the third party design tools that the designer is already familiar with.

# **SECTION 3**

- 1 Xilinx EPLD Products

- 2 Direct PAL Convesion Using Xilinx EPLDs

# 3 XC7200/A EPLD Family

- 4 XC7300 EPLD Family

- 5 Packages

- 6 Applications

- 7 Sales Offices

# XC7200 EPLD Family

| XC7236/XC7236A: 36 Macrocell CMOS EPLD | 3-1  |

|----------------------------------------|------|

| Ordering Information                   |      |

| XC7272: 72 Macrocell CMOS EPLD         | 3-17 |

| Ordering Information                   | 3-31 |

# XC7236/XC7236A 36 Macrocell CMOS EPLD

# **Preliminary Product Specifications**

### **Features**

- Second-Generation High Density Programmable Logic Device

- UV-erasable CMOS EPROM technology

- 36 Macrocells, grouped into four Function Blocks, interconnected by a programmable Universal Interconnect Matrix (UIM)

- Each Function Block contains a programmable ANDarray with up to 24 complementary inputs, providing up to 17 product terms per Macrocell

- Enhanced logic features

- Arithmetic Logic Unit in each Macrocell

- Dedicated fast carry network between Macrocells

- Wide AND capability in the Universal Interconnect Matrix

- Identical timing for all interconnect paths and for all Macrocell logic paths

- 36 signal pins

- 30 I/Os, 2 inputs, 4 outputs

- Each input is programmable

- Direct, latched, or registered

- I/O operation at 3.3 V or 5 V

- Meets JEDEC Standard (8-1A) for 3.3 V ± 0.3 V

- · Three high-speed, low-skew global clock inputs

- 44-pin plastic and windowed ceramic leaded chip carrier packages

# **General Description**

The XC7236/A is a second-generation High Density Programmable Logic Device that combines the classical features of the PAL-like EPLD architecture with innovative systems-oriented logic enhancements. This favors the implementation of fast state machines, large synchronous counters and fast arithmetic, as well as multi-level general-purpose logic. Performance, measured in achievable system clock rate and critical delays, is not only predictable, but independent of physical logic mapping, interconnect routing, and resource utilization. Performance, therefore, remains invariant between design iterations. The propagation delay through interconnect and logic is constant for any function implemented in any one of the output Macrocells.

The functional versatility of the traditional programmable logic array architecture is enhanced through additional

gating and control functions available in an Arithmetic Logic Unit (ALU) in each Macrocell. Dedicated fast arithmetic carry lines running directly between adjacent Macrocells and Function Blocks support fast adders, subtractors and comparators of any length up to 36 bits.

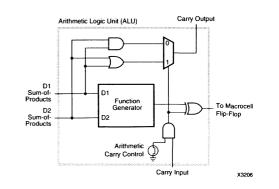

This additional ALU in each Macrocell can generate any combinatorial function of two sums of products, and it can generate and propagate arithmetic-carry signals between adjacent Macrocells and Functional Blocks.

The Universal Interconnect Matrix (UIM) facilitates unrestricted, fixed-delay interconnects from all device inputs and Macrocell outputs to any Function Block AND-array input. The UIM can also perform a logical AND across any number of its incoming signals on the way to any Function Block, adding another level of logic without additional delay. This supports bidirectional loadable synchronous counters of any size up to 36 bits, operating at the specified maximum device frequency

As a result of these logic enhancements, the XC7236/A can deliver high performance even in designs that combine large numbers of product terms per output, or need more layers of logic than AND-OR, or need a wide AND function in some of the product terms, or perform wide arithmetic functions.

Automated design mapping is supported by Xilinx development software based on design capture using third-party schematic entry tools, PLD compilers or direct text-based equation files. Design mapping is completed in a few minutes on a PC.

# **Architectural Overview**

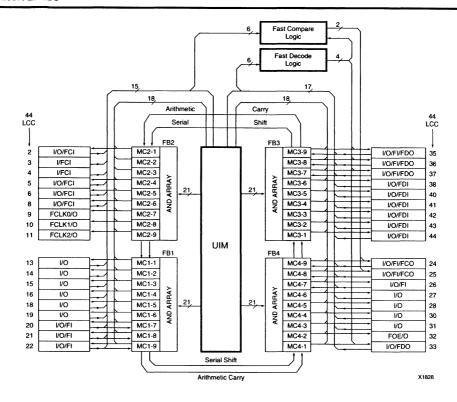

Figure 1 shows the XC7236/A structure. Four Function Blocks (FBs) are all interconnected by a central UIM. Each FB receives 21 signals from the UIM and each FB produces nine signals back into the UIM. All device inputs are also routed via the UIM to all FBs. Each FB contains nine output Macrocells (MCs) that draw from a programmable AND array driven by the 21 signals from the UIM. Most Macrocells drive a 3-state chip output; all feed back into the UIM.

The device also contains six dedicated FastCompare and FastDecode logic paths for address compare, decode or gating functions. The following pages describe the elements of this architecture in detail.

Figure 1. XC7236/A Architecture

# **Function Blocks and Macrocells**

The XC7236/A contains 36 Macrocells with identical structure, grouped into four Function Blocks of nine Macrocells each. Each Macrocell is driven by product terms derived from a programmable AND array in the Function Block. The AND array in each Function Block receives 21 signals and their complements from the UIM. In three Function Blocks, the AND array receives three additional inputs and their complements directly from FastInput (FI) pins, thus offering faster logic paths.

Five product terms are private to each Macrocell; an additional 12 product terms are shared among the nine Macrocells in each Function Block. Four of the private product terms can be selectively ORed together with up to four of the shared product terms, and drive the D1 input to the ALU. The other input, D2, to the ALU is driven by the

OR of the fifth private product term and up to eight of the remaining shared product terms.

As a programmable option, four of the private product terms can be used for other purposes. One of the private product terms can be used as a dedicated clock for the flipflop in the Macrocell. (See the subsequent description of other clocking options.) Another one of the private product terms can be the asynchronous active-High Reset of the Macrocell flip-flop, another one can be the asynchronous active-High Set of the Macrocell flip-flop, and another one can be the Output Enable signal.

As a configuration option, the Macrocell output can be fed back and ORed into the D2 input to the ALU after being ANDed with three of the shared product terms to implement counters and toggle flip-flops.

The ALU has two programmable modes: In the *logic mode*, it is a 2-input function generator, a 4-bit look-up table, that can be programmed to generate any Boolean function of its two inputs. It can OR them, widening the OR function to max 17 inputs; it can AND them, which means that one sum of products can be used to mask the other; it can XOR them, toggling the flip-flop or comparing the two sums of products. Either or both of the sum-of-product inputs to the ALU can be inverted and either or both can be ignored. The ALU can implement one additional layer of logic without any speed penalty.

In the *arithmetic mode*, the ALU block in each Macrocell can be programmed to generate the arithmetic sum or difference of two operands, combined with a carry signal coming from the next lower Macrocell. It also feeds a carry output to the next higher Macrocell. This carry propagation chain crosses the boundaries between Function Blocks. This dedicated carry chain overcomes the inherent speed and density problems of the traditional EPLD architecture, when trying to perform arithmetic functions.

The ALU output drives the D input of the Macrocell flip-flop. Each flip-flop has several programmable options. One option is to eliminate the flip-flop by making it transparent, which makes the Q output identical with the D input, independent of the clock. Otherwise, the flip-flop operates in the conventional manner, triggered by the rising edge on its clock input.

The clock source is programmable and is either the dedicated product term mentioned earlier, or one of two global FastCLK signals (FLCK0 or FLCK1) that are distributed with short delay and minimal skew over the whole chip.

The asynchronous Set and Reset (Clear) inputs override the clocked operation. If both asynchronous inputs are active simultaneously, Reset overrides Set. Upon powerup, each Macrocell flip-flop can be preloaded with either 0 or 1.

Figure 2. Function Block and Macrocell Schematic

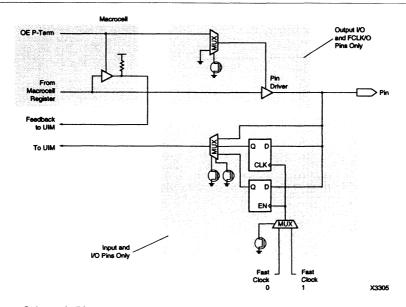

In addition to driving a chip output pin, the Macrocell output is also routed back as an input to the UIM. One private product term can be configured to control the Output Enable of the output pin driver and/or the feedback to the UIM. If configured to control UIM feedback, then when the OE product-term is de-asserted, the UIM feedback line is forced High and thus disabled.

### **Universal Interconnect Matrix**

The UIM receives 68 inputs: 36 from the Macrocell feedbacks, 30 from bidirectional I/O pins, and 2 from dedicated input pins. Acting as an unrestricted crossbar switch, the UIM generates 84 output signals, 21 to each Function Block.

Any one of the 68 inputs can be programmed to be connected to any number of the 84 outputs. The delay through the array is constant, independent of the apparent routing distance, the fan-out, fan-in, or routing complexity.

Routability is not an issue in that any UIM input can drive any UIM output or multiple outputs without additional delay.

When multiple inputs are programmed to be connected to the same output, this output becomes the AND of the input signals if the levels are interpreted as active High. By choosing the appropriate signal inversion at the input pin, Macrocell outputs and Function Block AND-array input, this AND-logic can also be used to implement a NAND,

OR, or NOR function. This offers an additional level of logic without any speed penalty.

A Macrocell feedback signal that is disabled by the output enable product term represents a High input to the UIM. Several such Macrocell outputs programmed onto the same UIM output thus emulate a 3-state bus line. If one of the Macrocell outputs is enabled, the UIM output assumes that same level.

# **Outputs**

Thirty-four of the 36 Macrocell drive chip outputs directly through individually programmable inverters followed by 3-state output buffers; each can be individually controlled by the Output Enable product term mentioned above. An additional configuration option disables the output permanently. One dedicated FastOE input can also be configured to control any of the chip outputs instead of, or in conjunction with the individual OE product term.

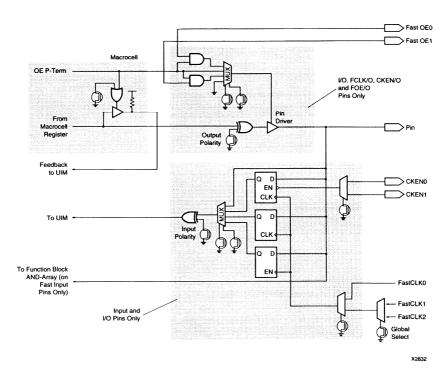

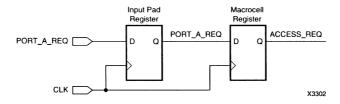

### Inputs

Each signal input to the chip is programmable as either direct, latched, or registered in a flip flop. Latch and flip-flop can be programmed with either of two FastCLK signals as latch enable or clock. The two FastCLK signals are FCLK0 and a global choice of either FCLK1 or FCLK2. Latches are transparent when FastCLK is High, and flip-flops clock on the rising edge of FastCLK. Registered inputs allow high system clock rates by pipelining the inputs before they

Figure 3. Input/Output Schematic

incur the combinatorial delay in the device, provided the one-clock-period pipeline latency is acceptable.

The direct, latched, or registered inputs then drive the UIM. There is no propagation-delay difference between pure inputs and I/O inputs.

# 3.3 V or 5 V Interface configuration

The XC7236/A can be used in systems with two different supply voltages, 5 V or 3.3 V. The device has separate V $_{\rm CC}$  connections to the internal logic and input buffers (V $_{\rm CCINT}$ ) and to the I/O output drivers (V $_{\rm CCIO}$ ). V $_{\rm CCINT}$  is always connected to a nominal +5 V supply, but V $_{\rm CCIO}$  may be connected to either +5 V or +3.3 V, depending on the output interface requirement.

When  $V_{\rm CCIO}$  is connected to +5 V, the input thresholds are TTL levels, and thus compatible with 5 V or 3.3 V logic, and

the output high levels are compatible with 5 V systems. When V<sub>CCIO</sub> is connected to 3.3 V, the input thresholds are still TTL levels, and the outputs pull up to the 3.3 V rail. This makes the XC7236/A ideal for interfacing directly to 3.3 V components. In addition, the output structure is designed such that the I/O can also safely interface to a mixed 3.3-V or 5-V bus.

# FastDecode and FastCompare

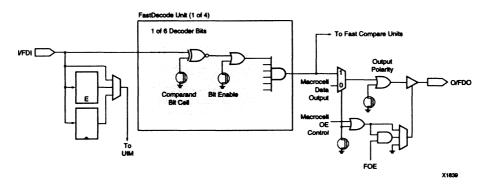

The FastDecode unit contains four fast programmable 6-bit decoders with a common set of six inputs (FDI). Each decoder compares the data on the inputs against a pre-programmed 6-bit fixed value and drives a designated chip output (FDO). Each decoder is programmable with Don't Care bits, and each can indicate match either active High or Low as a programmable option.

Figure 4a. FastDecode Schematic

Figure 4b. FastCompare Schematic

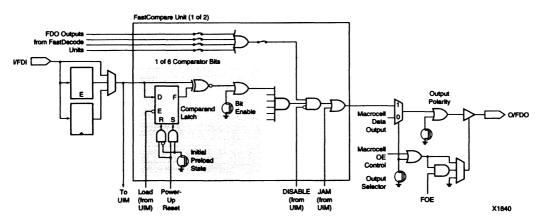

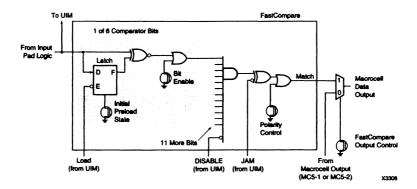

The FastCompare unit contains two fast programmable 6-bit comparators with a common set of six inputs (FCI), separate from the FDI inputs . Each comparator compares the data on the inputs against a pattern stored in its six latches and drives a designated chip output (FCO). Data can be loaded into these latches either from the FastCompare data inputs, or can be preloaded during chip configuration (Power-up or Reset). Each comparator is programmable with Don't Care bits and can be conditioned with the result of one or more of the FastDecode FDO outputs.

The comparison can be disabled (forced false) and the polarity of the match response can be chosen.

Since this compare circuitry bypasses the UIM and Macrocells, it is very fast and can also be used as high-speed address decoder.

# Programming and Using the XC7236/A

The features and capabilities described above are used by the Xilinx development software to program the device according to the specification given either through schematic entry, or through a behavioral description expressed in Boolean equations.

The user can specify a security bit that prevents any reading of the programming bit map after the device has been programmed and verified.

The device is programmed in a manner similar to an EPROM (ultra-violet light erasable read-only memory) using the Intel Hex format. Programming support is available from a number of programmer manufacturers. The UIM connections and Function Block AND-array connections are made directly by non-volatile EPROM cells. Other control bits are read out of the EPROM array and stored into latches just after power-up. This method, common among EPLD devices, requires either a very fast

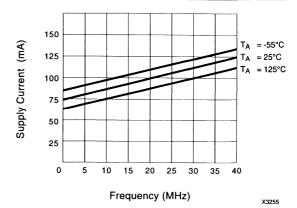

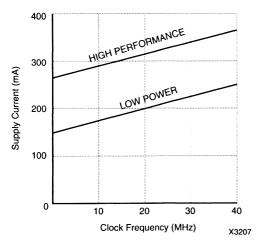

Typical Power Requirements for XC7236/A Configured as Eight 4-bit Counters ( $V_{CC} = +5.0 \text{ V}$ ,  $V_{IN} = 0 \text{ or } 5 \text{ V}$ , all outputs open)

$V_{CC}$  rise time (<5  $\mu s$ ) or the application of a master-reset signal delayed at least until  $V_{CC}$  has reached the required operating voltage. The latter can be achieved using a simple capacitor and pull-up resistor on the MR pin (the RC product should be larger than twice the  $V_{CC}$  rise time). The power-up or reset signal initiates a self-timed configuration period lasting about 350  $\mu s$  (t $_{RESET}$ ), during which all device outputs remain disabled and programmed preload state values are loaded into the Macrocell registers.

Unused input and I/O pins should be tied to ground or Vcc or some valid logic level. This is common practice for all CMOS devices to avoid dissipating excess current through the input pad circuitry.

The recommended decoupling capacitance on the three  $V_{CC}$  pins should total 1  $\mu F$  using high-speed (tantalum or ceramic) capacitors.

# **Absolute Maximum Ratings**

| Symbol           | Parameter                                                | Value        | Units |

|------------------|----------------------------------------------------------|--------------|-------|

| v <sub>cc</sub>  | Supply voltage relative to GND                           | -0.5 to 7.0  | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND                        | -0.5 to 7.0  | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output                        | -0.5 to 7.0  | V     |

| T <sub>STG</sub> | Storage temperature                                      | -65 to + 150 | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in. = 1.5 mm) | + 260        | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

# **Operating Conditions**

| Symbol             | Parameter                                                                    | Min  | Max                   | Units |

|--------------------|------------------------------------------------------------------------------|------|-----------------------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND Commercial t <sub>A</sub> = 0°C to 70°C       | 4.75 | 5.25                  | ٧     |

| V <sub>CCIO</sub>  | Supply voltage relative to GND Industrial $t_A = -40$ °C to 85°C             | 4.5  | 5.5                   | V     |

|                    | Supply voltage relative to GND Military $t_c = -55^{\circ}\text{C}$ to 125°C | 4.5  | 5.5                   | ٧     |

| V <sub>ccio</sub>  | I/O supply voltage 3.3 V                                                     | 3.0  | 3.6                   | ٧     |

| V <sub>IL</sub>    | Low-level input voltage                                                      | 0    | 0.8                   | ٧     |

| V <sub>IH</sub>    | High-level input voltage                                                     | 2.0  | V <sub>cc</sub> + 0.3 | ٧     |

| v <sub>o</sub>     | Output voltage                                                               | 0    | V <sub>CCIO</sub>     | ٧     |

# **DC Characteristics Over Operating Conditions**

| Symbol          | Parameter                         | Test Conditions                                                     | Min | Max | Units |

|-----------------|-----------------------------------|---------------------------------------------------------------------|-----|-----|-------|

| $V_{OH}$        | 5 V TTL high-level output voltage | I/O = -4.0 mA<br>V <sub>CC</sub> = Min                              | 2.4 |     | V     |

|                 | 3.3 V high-level output           | I/O = -3.2 mA<br>V <sub>CC</sub> = Min                              | 2.4 |     | V     |

| $V_{OL}$        | 5 V low-level output voltage      | I/O = 12 mA<br>V <sub>CC</sub> = Min                                |     | 0.5 | ٧     |

|                 | 3.3 V low-level output voltage    | I/O = 10 mA<br>V <sub>CC</sub> = Min                                |     | 0.4 | V     |

| I <sub>cc</sub> | Supply Current                    | $V_{IN} = 0 V$<br>$V_{CC} = Max f = 0 MHz$                          |     | 100 | μА    |

| I <sub>IL</sub> | Input leakage current             | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = GND or V <sub>CCIO</sub> |     | ±10 | μА    |

| l <sub>oz</sub> | Output High-Z leakage current     | V <sub>CC</sub> = Max<br>V <sub>O</sub> = GND or V <sub>CCIO</sub>  |     | ±10 | μА    |

| C <sub>IN</sub> | Input capacitance (sample tested) | V <sub>IN</sub> = GND<br>f = 1.0 MHz                                |     | 10  | pF    |

| AC Timing Requirements                                                                  | [    |                               |     | XC7236    |     |     |     | XC7236A |     |          |       |

|-----------------------------------------------------------------------------------------|------|-------------------------------|-----|-----------|-----|-----|-----|---------|-----|----------|-------|

|                                                                                         | Snoo | d Grade                       |     | XC/<br>30 | T   | 25  | -2  |         | -1  | <u> </u> |       |

|                                                                                         | Spee | T                             |     |           |     | 25  | -2  | .0      |     | d Only)  |       |

| Description                                                                             | Fig. | Symbol                        | Min | Max       | Min | Max | Min | Max     | Min | Max      | Units |

| Sequential toggle frequency (with feedback) using FastCLK                               | 5    | f <sub>CYC</sub> (Note 1)     | 0   | 33        | 0   | 40  | 0   | 50      | 0   | 60       | MHz   |

| Sequential toggle frequency (with feedback) using a Product-Term clock                  | 5    | f<br>CYC1<br>(Note 1)         | 0   | 33        | 0   | 40  | 0   | 50      | 0   | 60       | MHz   |

| Macrocell toggle frequency using local feedback and FastCLK                             |      | f <sub>CYC4</sub><br>(Note 5) | 0   | 42        | 0   | 50  | 0   | 50      | 0   | 60       | MHz   |

| Macrocell register transmission frequency (without feedback) using FastCLK              |      | f <sub>CLK</sub><br>(Note 5)  | 0   | 36        | 0   | 45  | 0   | 50      | 0   | 60       | MHz   |

| Macrocell register transmission frequency (without feedback) using a Product-Term clock |      | f<br>CLK1<br>(Note 5)         | 0   | 36        | 0   | 42  | 0   | 50      | 0   | 60       | MHz   |

| Input register transmission frequency (without feedback) using FastCLK                  |      | f<br>CLK2<br>(Note 5)         | 0   | 42        | 0   | 50  | 0   | 50      | 0   | 60       | MHz   |

| Input register to Macrocell register pipeline freq. using FastCLK                       | 6    | f <sub>CLK3</sub><br>(Note 1) | 0   | 25        | 0   | 33  | 0   | 40      | 0   | 60       | MHz   |

| FastCLK Pulse width (High/Low)                                                          | 10   | t <sub>w</sub>                | 12  |           | 10  |     | 8   |         | 6   |          | ns    |

| Product-Term clock pulse width (active/inactive)                                        | 10   | t <sub>w1</sub>               | 14  |           | 12  |     | 9   |         | 7   |          | ns    |

| Input to Macrocell register set-up time before FastCLK                                  | 8    | t <sub>su</sub>               | 35  |           | 29  |     | 24  |         | 18  |          | ns    |

| Input to Macrocell register hold time after FastCLK                                     | 8    | t <sub>H</sub>                | -7  |           | -7  |     | -4  |         | -4  |          | ns    |

| Input to Macrocell register set-up time before Product-Term clock                       | 7    | t <sub>SU1</sub><br>(Note 1)  | 19  |           | 16  |     | 14  |         | 10  |          | ns    |

| Input to Macrocell register hold time after Product-Term clock                          | 7    | t <sub>H1</sub>               | 0   |           | 0   |     | 0   |         | 0   |          | ns    |

| Input register/latch set-up time before FastCLK                                         | 9    | t <sub>SU2</sub>              | 10  |           | 8   |     | 8   |         | 6   |          | ns    |

| Input register/latch hold time<br>after FastCLK                                         | 9    | t <sub>H2</sub>               | 0   |           | 0   |     | 0   |         | 0   |          | ns    |

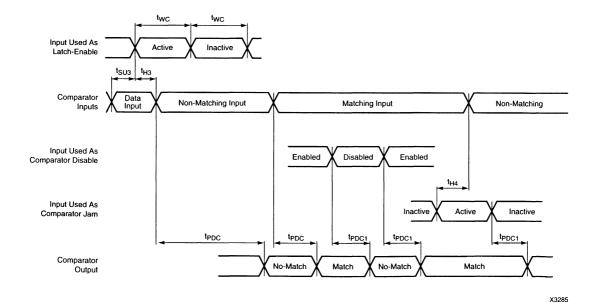

| FastCompare input set-up time before latch-enable input                                 | 11   | t <sub>su3</sub>              | 4   |           | 2   |     | 2   |         | 2   |          | ns    |

| FastCompare input hold time after latch-enable input                                    | 11   | t <sub>H3</sub>               | 18  |           | 14  |     | 14  |         | 12  |          | ns    |

| FastCompare input hold time after comparator jam asserted                               | 11   | t <sub>H4</sub>               | 30  |           | 25  |     | 25  |         | 22  |          | ns    |

| FastInput to Macrocell register set-up time before FastCLK                              |      | t <sub>SU5</sub>              | 26  |           | 20  |     | 18  |         | 15  |          | ns    |

| FastInput to Macrocell register hold time after FastCLK                                 |      | t <sub>H5</sub>               | 0   |           | 0   |     | 0   |         | 0   |          | ns    |

| Set/reset pulse width (active)                                                          | 10   | t <sub>wa</sub>               | 15  |           | 12  |     | 12  |         | 10  |          | ns    |

| Set/reset input recovery set-up time before FastCLK                                     | 10   | t <sub>RA</sub>               | 36  |           | 30  |     | 25  |         | 20  |          | ns    |

| AC Timing Requirements (Continued)                 |      |                  |     |     |      |     |         |     |         |                |       |

|----------------------------------------------------|------|------------------|-----|-----|------|-----|---------|-----|---------|----------------|-------|

| . , , ,                                            |      |                  |     | XC7 | 7236 |     | XC7236A |     |         |                |       |

|                                                    | Spee | d Grade          | -3  | 30  | -:   | 25  | -2      | 20  | (Com/li | 16<br>nd Only) |       |

| Description                                        | Fig. | Symbol           | Min | Max | Min  | Max | Min     | Max | Min     | Max            | Units |

| Set/reset input hold time after FastCLK            | 10   | t <sub>HA</sub>  | -5  |     | -5   |     | 0       |     | 0       |                | ns    |

| Set/reset input recovery time before P-Term clock  | 10   | t <sub>RA1</sub> | 18  |     | 15   |     | 15      |     | 12      |                | ns    |

| Set/reset input hold time after P-Term clock       | 10   | t <sub>HA1</sub> | 12  |     | 9    |     | 9       |     | 8       |                | ns    |

| Set/reset input hold time after reset/set inactive |      | t <sub>HRS</sub> | 12  |     | 10   |     | 10      |     | 8       |                | ns    |

| FastCompare latch-enable pulse width               | 10   | t <sub>wc</sub>  | 22  |     | 16   |     | 16      |     | 12      |                | ns    |

| opagation Delays                                          |      |                             |        |     |     |     |         | V07 | 0004                  |     | 1     |

|-----------------------------------------------------------|------|-----------------------------|--------|-----|-----|-----|---------|-----|-----------------------|-----|-------|

|                                                           |      |                             | XC7236 |     |     |     | XC723EA |     |                       |     |       |

|                                                           | Spee | d Grade                     | -30    |     | -25 |     | -20     |     | -16<br>(Com/Ind Only) |     |       |

| Description                                               | Fig. | Symbol                      | Min    | Max | Min | Max | Min     | Max | Min                   | Max | Units |

| FastCLK input to registered output delay                  | 10   | t <sub>co</sub>             | 5      | 17  | 5   | 14  | 3       | 13  | 3                     | 10  | ns    |

| P-Term clock input to registered output delay             | 10   | t <sub>CO1</sub>            | 10     | 36  | 10  | 30  | 5       | 24  | 5                     | 20  | ns    |

| Set/reset input to registered output delay                | 10   | t <sub>AO</sub>             | 10     | 48  | 10  | 40  | 5       | 32  | 5                     | 25  | ns    |

| Input to nonregistered output delay                       | 10   | t <sub>PD</sub><br>(Note 1) | 10     | 48  | 10  | 40  | 5       | 32  | 5                     | 25  | ns    |

| FastCompare or FastDecode input to FastCompare output     | 11   | t <sub>PDC</sub>            | 5      | 26  | 5   | 23  | 3       | 23  | 3                     | 20  | ns    |

| FastCompare DISABLE or JAM input to<br>FastCompare output | 11   | t <sub>PDC1</sub>           | 5      | 30  | 5   | 25  | 3       | 24  | 3                     | 22  | ns    |

| FastDecode data input to FastDecode output delay          |      | t <sub>PDC3</sub>           | 5      | 18  | 5   | 15  | 3       | 15  | 3                     | 14  | ns    |

| Input to output enable                                    | 10   | t <sub>OE</sub>             | 10     | 37  | 10  | 32  | 5       | 25  | 5                     | 20  | ns    |

| Input to output disable                                   | 10   | t <sub>op</sub>             | 10     | 37  | 10  | 32  | 5       | 25  | 5                     | 20  | ns    |

| FastInput to non-registered Macrocell output delay        |      | t <sub>PD5</sub>            | 10     | 39  | 10  | 31  | 5       | 25  | 5                     | 20  | ns    |

| FastInput to output enabled                               |      | t <sub>OE5</sub>            | 5      | 28  | 5   | 23  | 3       | 20  | 3                     | 15  | ns    |

| FastInput to output disabled                              |      | t <sub>OD5</sub>            | 5      | 28  | 5   | 23  | 3       | 20  | 3                     | 15  | ns    |

| FOE input to output enabled                               |      | t <sub>FOE</sub>            | 5      | 18  | 5   | 15  | 3       | 14  | 3                     | 12  | ns    |

| FOE input to output disabled                              |      | t <sub>FOD</sub>            | 5      | 18  | 5   | 15  | 3       | 14  | 3                     | 12  | ns    |

Notes: 1. Specifications account for logic paths which use the maximum number of available product terms and the ALU.

| Increm | ental | Para | meters |

|--------|-------|------|--------|

|        |       |      |        |

|                                                                                                         |      |                                                   | ;   | XC  | 7236 |     | XC7236A |     |               |              |       |

|---------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|-----|-----|------|-----|---------|-----|---------------|--------------|-------|

|                                                                                                         | Spee | d Grade                                           | -3  | 0   | -2   | 25  | -2      | 20  | -1<br>(Com/In | 6<br>d Only) |       |

| Description                                                                                             | Fig  | Symbol                                            | Min | Max | Min  | Max | Min     | Max | Min           | Max          | Units |

| Arithmetic carry delay between adjacent Macrocells                                                      | 12   | t <sub>PDT1</sub> (Note 2)                        |     | 1.5 |      | 1.2 |         | 1.2 |               | 1            | ns    |

| Arithmetic carry delay<br>through 9 adjacent Macrocells in a Function Block                             | 12   | t <sub>PDT8</sub><br>(Note 2)                     |     | 8   |      | 6   |         | 5   |               | 3            | ns    |

| Arithmetic carry delay through 10 Macrocells from Macrocell #n to Macrocell #n in next F Block          | 12   | t <sub>PDT9</sub> (Note 2)                        |     | 12  |      | 9   |         | 6   |               | 4            | ns    |

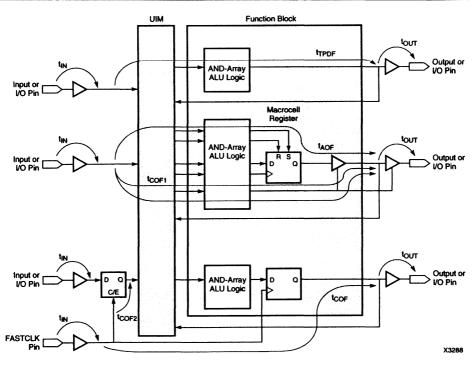

| Incremental delay from UIM-input<br>(for P-Term clock) to registered Macrocell<br>feedback              | 13   | t <sub>COF1</sub>                                 |     | 14  |      | 12  |         | 7   |               | 5            | ns    |

| Incremental delay from FastCLK net to latched/registered UIM-input                                      | 13   | t<br>COF2<br>(Note 3)                             |     | 1   |      | 1   |         | 1   |               | 1            | ns    |

| Incremental delay from UIM-input to nonregistered Macrocell feedback                                    | 13   | t <sub>PDF</sub> (Note 1)                         |     | 26  |      | 22  |         | 14  |               | 10           | ns    |

| Incremental delay from UIM-input (set/reset) to registered Macrocell feedback                           | 13   | t <sub>AOF</sub>                                  |     | 26  |      | 22  |         | 14  |               | 10           | ns    |

| Incremental delay from UIM-input<br>(used as output-enable/disable)<br>to Macrocell feedback            | 13   | t <sub>OEF</sub> ,<br>t <sub>ODF</sub>            |     | 15  |      | 14  |         | 7   |               | 5            | ns    |

| Propagation delay<br>through unregistered Input pad (to UIM)<br>plus output pad driver (from Macrocell) | 13   | t <sub>IN</sub> +<br>t <sub>OUT</sub><br>(Note 4) |     | 22  |      | 18  |         | 18  |               | 15           | ns    |

# Power-up/Reset Timing Parameters

| Description                                             | Symbol                     | Min | Тур | Max  | Units |

|---------------------------------------------------------|----------------------------|-----|-----|------|-------|

| Master Reset input Low pulse width                      | t <sub>wmR</sub>           | 100 |     |      | ns    |

| V <sub>CC</sub> rise time (if MR not used for power-up) | t <sub>rVCC</sub> (Note 6) |     |     | 5    | μs    |

| Configuration completion time (to outputs operational)  | t <sub>RESET</sub>         |     | 350 | 1000 | μs    |

Notes: 1. Specifications account for logic paths which use the maximum number of available product terms and the ALU.

- 2. Arithmetic carry delays are measured as the increase in required set-up time to adjacent Macrocell(s) for an adder with registered outputs.

- 3. Parameter  $t_{COF2}$  is derived as the difference between the clock period for pipelining input-to-Macrocell registers (1/ $t_{CLK3}$ ) and the non-registered input set-up time ( $t_{SU}$ ).

- 4. Parameter t<sub>IN</sub> represents the delay from an input or I/O pin to a UIM-input (or from a FastCLK pin to the Fast CLK net); tout represents the delay from a Macrocell output (feedback point) to an output or I/O pin. Only the sum of t<sub>IN</sub> + t<sub>OUT</sub> can be derived from measurements, e.g., t<sub>IN</sub> + t<sub>OUT</sub> = t<sub>SU</sub> + t<sub>CO</sub> - 1/f<sub>CYC</sub>.

5. Not tested but derived from appropriate pulse-widths, set-up time and hold-time measurements.

- Due to the synchronous operation of the power-up reset and the wide range of ways V<sub>cc</sub> can rise to its steady state, V<sub>cc</sub> rise *must be* monotonic. Following reset, the Clock, Reset and Set inputs must not be asserted until all applicable input and feedback set-up times are met.

# **Timing and Delay Path Specifications**

The delay path consists of three blocks that can be connected in series:

- . Input Buffer and associated latch or register

- Logic Resource (UIM, AND-array and Macrocell)

- · Three-state Output Buffer

All inputs have the same delay, regardless of fan-out or location. All logic resources have the same delay, regardless of logic complexity, interconnect topology or location on the chip. All outputs have the same delay. The achievable clock rate is, therefore, determined only by the input method (direct, latched or registered) and the number of times a signal passes through the combinatorial logic.

### **Timing and Delay Path Descriptions**

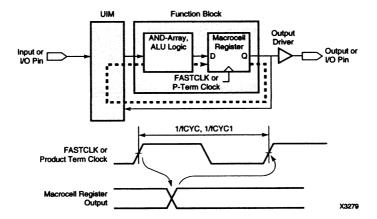

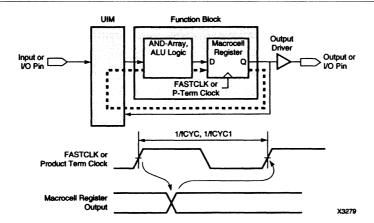

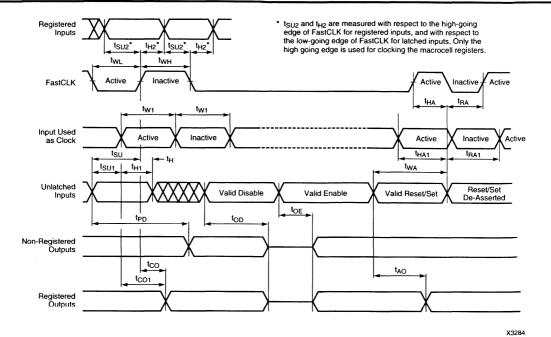

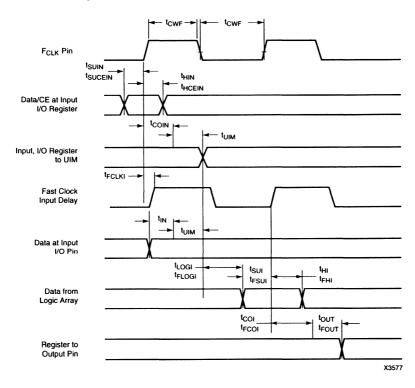

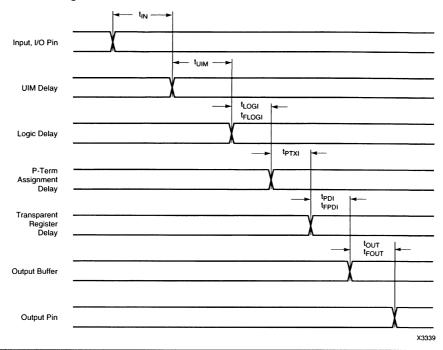

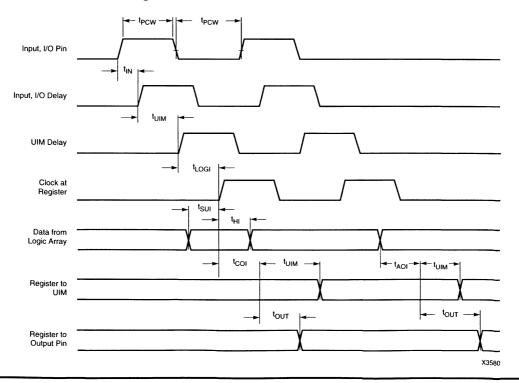

Figure 5 defines the max clock frequency (with feedback). Any Macrocell output can be fed back to the UIM as an input for the next clock cycle. The parameters  $f_{\rm CYC1}$  and  $f_{\rm CYC1}$  specify the maximum operating frequency for FastCLK and product-term clock operation respectively.

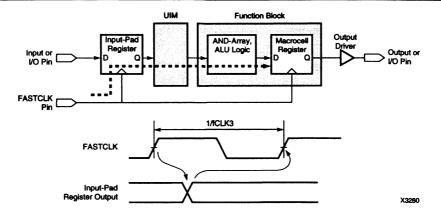

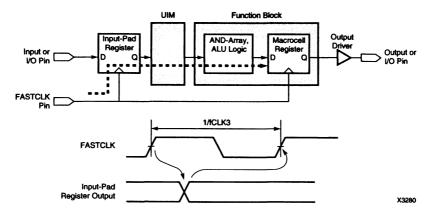

Figure 6 specifies the max operating frequency ( $f_{\rm CLK3}$ )for pipelined operation between the input registers and the Macrocell registers, using FastCLK.

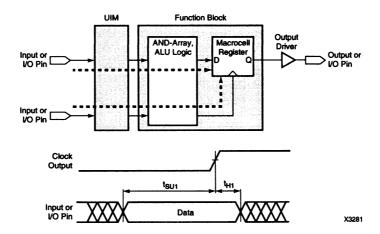

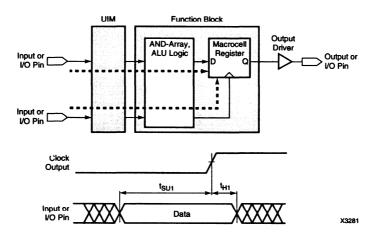

Figure 7 defines the set-up and hold times from the data inputs to the product-term clock used by the output register.

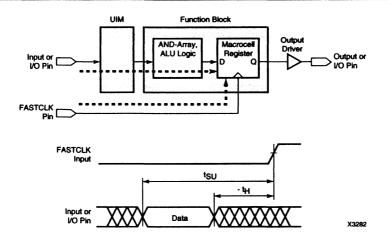

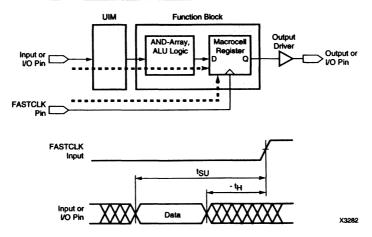

Figure 8 defines the set-up and hold times from the data inputs to the FastCLK used by the output register.

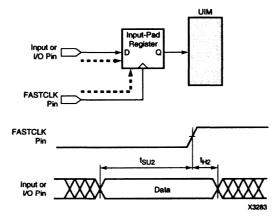

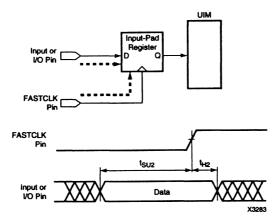

Figure 9 defines the set-up and hold times from the data input to the FastCLK used in an input register.

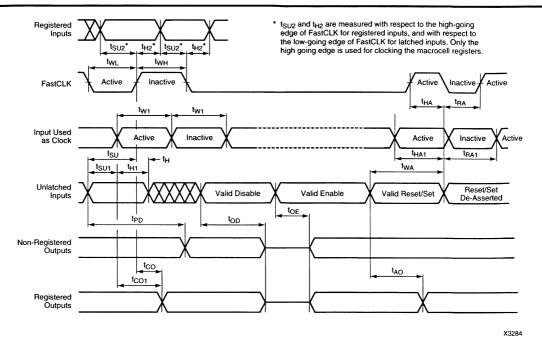

Figure 10 shows the waveforms for the Macrocell and control paths.

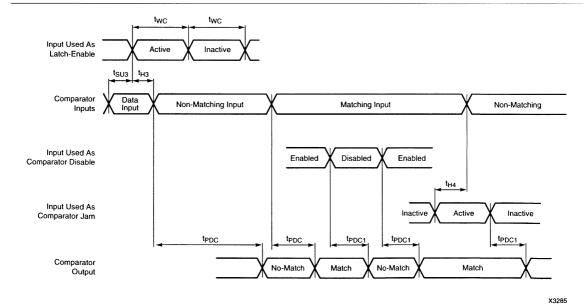

Figure 11 defines the FastCompare timing parameters.

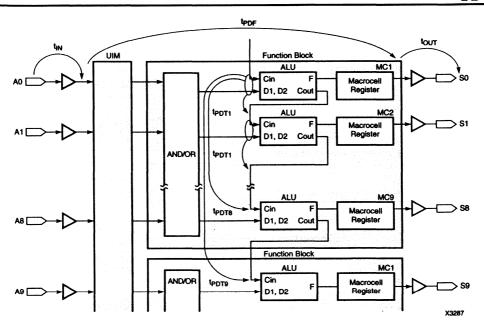

Figure 12 defines the carry propagation delays between Macrocells and between Function Blocks. The parameters describe the delay from the CIN, D1 and D2 inputs of a Macrocell ALU to the CIN input of the adjacent Macrocell ALU. These delays must be added to the standard Macrocell delay path ( $t_{\rm PD}$  or  $t_{\rm SU}$ )to determine the performance of an arithmetic function.

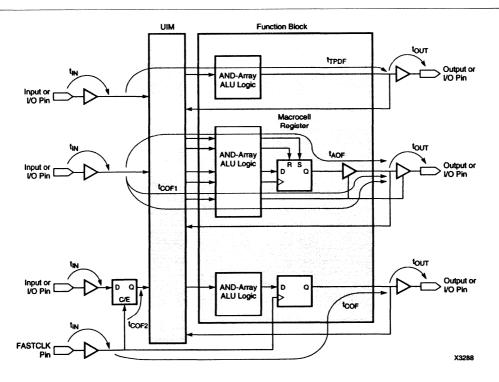

Figure 13 defines the incremental parameters for the standard Macrocell logic paths. These incremental parameters are used in conjunction with pin-to-pin parameters when calculating compound logic path timing. Incremental parameters are derived indirectly from other pin-to-pin measurement.

Figure 5. Delay Path Specifications for  $f_{\rm CYC}$  and  $f_{\rm CYC1}$

Figure 6. Delay Path Specification for f<sub>CLK3</sub>

Figure 7. Delay Path Specification for  $\mathbf{t}_{\text{SU1}}$  and  $\mathbf{t}_{\text{H1}}$

Figure 8. Delay Path Specification for  $\mathbf{t}_{\mathrm{SU}}$  and  $\,\mathbf{t}_{\mathrm{H}}$

Figure 9. Delay Path Specification for  $t_{\rm SU2}$  and  $t_{\rm H2}$

Figure 10. Principal Pin-to-Pin Measurements

Figure 11. FastCompare Timing Waveforms

Figure 12. Arithmetic Timing Parameters

Figure 13. Incremental Timing Parameters

### 44-Pin LCC Pinouts

| Pin # | Input        |                   | Output |

|-------|--------------|-------------------|--------|

| 1     | Master Reset | V <sub>PP</sub>   |        |

| 2     | Input/FCI    |                   | MC2-1  |

| 3     | Input/FCI    |                   |        |

| 4     | Input/FCI    |                   |        |

| 5     | Input/FCI    |                   | MC2-4  |

| 6     | Input/FCI    |                   | MC2-5  |

| 7     |              | GND               |        |

| 8     | Input/FCI    |                   | MC2-6  |

| 9     | FastCLK0     |                   | MC2-7  |

| 10    | FastCLK1     |                   | MC2-8  |

| 11    | FastCLK2     |                   | MC2-9  |

| 12    |              | V <sub>CCIO</sub> |        |

| 13    | Input        |                   | MC1-1  |

| 14    | Input        |                   | MC1-2  |

| 15    | Input        |                   | MC1-3  |

| 16    | Input        |                   | MC1-4  |

| 17    |              | GND               |        |

| 18    | Input        |                   | MC1-5  |

| 19    | 19 Input     |                   | MC1-6  |

| 20    | 20 Input/FI  |                   | MC1-7  |

| 21    | Input/FI     |                   | MC1-8  |

| 22    | 2 Input/Fi   |                   | MC1-9  |

| Pin # | Input     | Output             |

|-------|-----------|--------------------|

| 23    |           | V <sub>CCIO</sub>  |

| 24    | Input/FI  | MC4-9/FCO          |

| 25    | Input/FI  | MC4-8/FCO          |

| 26    | Input/FI  | MC4-7              |

| 27    | Input     | MC4-6              |

| 28    | Input     | MC4-5              |

| 29    |           | GND                |

| 30    | Input     | MC4-4              |

| 31    | Input     | MC4-3              |

| 32    | FastOE    | MC4-2              |

| 33    | Input     | MC4-1/FDO          |

| 34    |           | V <sub>CCINT</sub> |

| 35    | Input/FI  | MC3-9/FDO          |

| 36    | Input/FI  | MC3-8/FDO          |

| 37    | Input/FI  | MC3-7/FDO          |

| 38    | Input/FDI | MC3-6              |

| 39    |           | GND                |

| 40    | Input/FDI | MC3-5              |

| 41    | Input/FDI | MC3-4              |

| 42    | Input/FDI | MC3-3              |

| 43    | Input/FDI | MC3-2              |

| 44    | Input/FDI | MC3-1              |

FI = Fast Input FCI = FastCompare input FDI = FastDecode input

FCO = FastCompare output FDO = FastDecode output

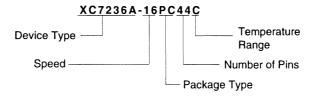

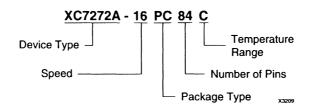

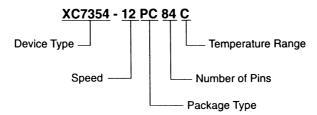

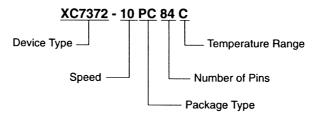

## **Ordering Information**

#### **Device Options**

XC7236 XC7236A

## **Speed Options**

XC7236 -30 30 ns (33 MHz) sequential cycle time

-25 25 ns (40 MHz) sequential cycle time

XC7236A -25 25 ns (40 MHz) sequential cycle time

-20 20 ns (50 MHz) sequential cycle time

-16 16 ns (60 MHz) sequential cycle time (commercial and industrial only)

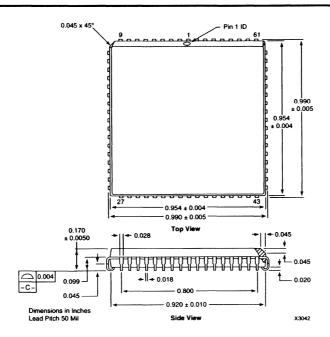

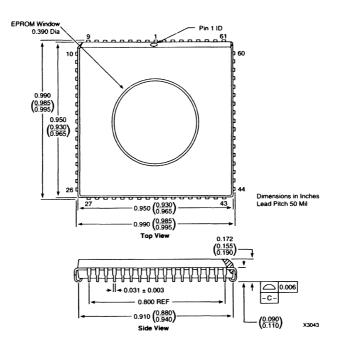

## **Package Options**

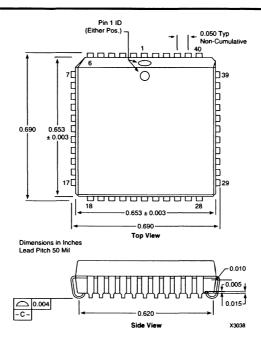

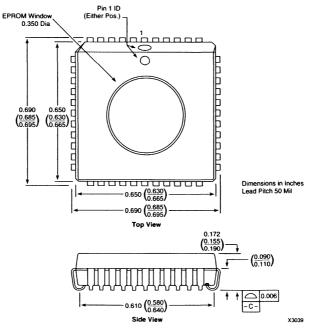

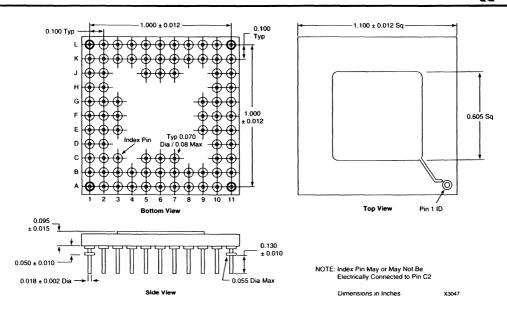

PC44 44-Pin Plastic Leaded Chip Carrier

WC44 44-Pin Windowed Ceramic Leaded

Chip Carrier

#### **Temperature Options**

C Commercial 0°C to 70°C I Industrial -40°C to 85°C M Military -55°C to 125°C (Case)

## XC7272A 72 Macrocell CMOS EPLD

## **Preliminary Product Specifications**

#### **Features**

- Second-Generation High Density Programmable Logic Device

- UV-erasable CMOS EPROM technology

- 72 Macrocells, grouped into eight Function Blocks, interconnected by a programmable Universal Interconnect Matrix

- Each Function Block contains a programmable ANDarray with 21 complementary inputs, providing up to 16 product terms per Macrocell

- · Enhanced logic features:

- 2-input Arithmetic Logic Unit in each Macrocell

- Dedicated fast carry network between Macrocells

- Wide AND capability in the Universal Interconnect Matrix

- Identical timing for all interconnect paths and for all Macrocell logic paths

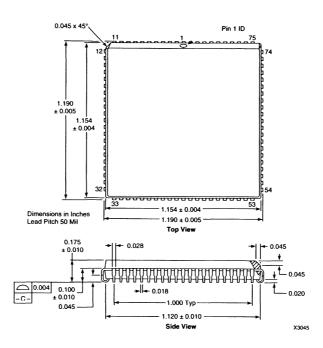

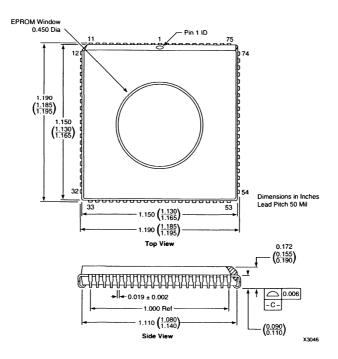

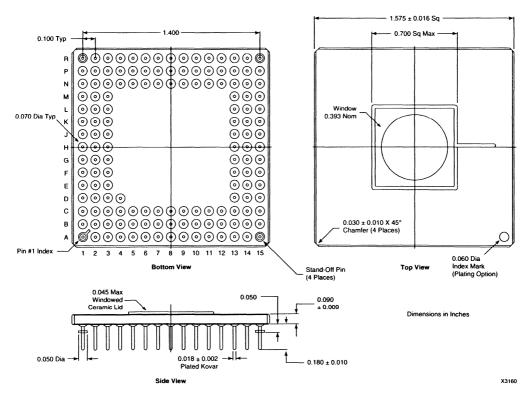

- 72 signal pins in the 84-pin packages

42 I/Os, 12 inputs, 18 outputs

- Each input is programmable

Direct, latched, or registered

- I/O-pin is usable as input when Macrocell is buried

- Two high-speed, low-skew global clock inputs

- 68-pin and 84-pin leaded chip carrier packages and 84-pin Pin-Grid-Array packages

#### **General Description**

The XC7272A is a second-generation High Density Programmable Logic Device that combines the classical features of the PAL-like EPLD architecture with innovative systems-oriented logic enhancements. This favors the implementation of fast state machines, large synchronous counters and fast arithmetic, as well as multi-level general-purpose logic. Performance, measured in achievable system clock rate and critical delays, is not only predictable, but independent of physical logic mapping, interconnect routing, and resource utilization. Performance, therefore, remains invariant between design iterations. The propagation delay through interconnect and logic is constant for any function implemented in any one of the output Macrocells.

The functional versatility of the traditional programmable logic array architecture is enhanced through additional

gating and control functions available in an Arithmetic Logic Unit (ALU) in each Macrocell. Dedicated fast arithmetic carry lines running directly between adjacent Macrocells and Function Blocks support fast adders, subtractors and comparators of any length up to 72 bits.

This additional ALU in each Macrocell can generate any combinatorial function of two sums of products, and it can generate and propagate arithmetic-carry signals between adjacent Macrocells and Functional Blocks.

The Universal Interconnect Matrix (UIM) facilitates unrestricted, fixed-delay interconnects from all device inputs and Macrocell outputs to any Function Block AND-array input. The UIM can also perform a logical AND across any number of its incoming signals on the way to any Functional Block, adding another level of logic without additional delay. This supports bidirectional loadable synchronous counters of any size up to 72 bits, operating at the specified maximum device frequency

As a result of these logic enhancements, the XC7272A can deliver high performance even in designs that combine large numbers of product terms per output, or need more layers of logic than AND-OR, or need a wide AND function in some of the product terms, or perform wide arithmetic functions.

Automated design mapping is supported by Xilinx development software based on design capture using third-party schematic entry tools, PLD compilers or direct text-based equation files. Design mapping is completed in a few minutes on a PC.

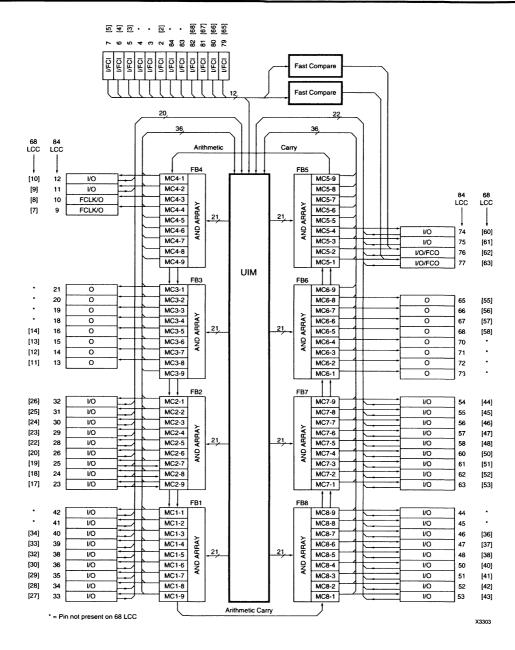

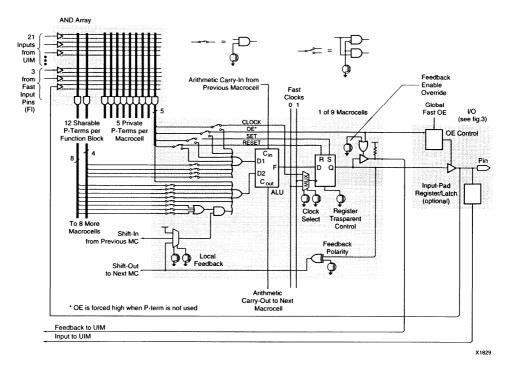

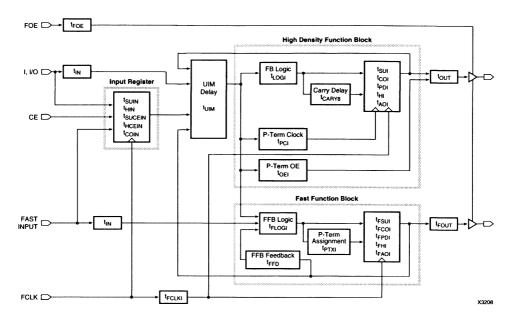

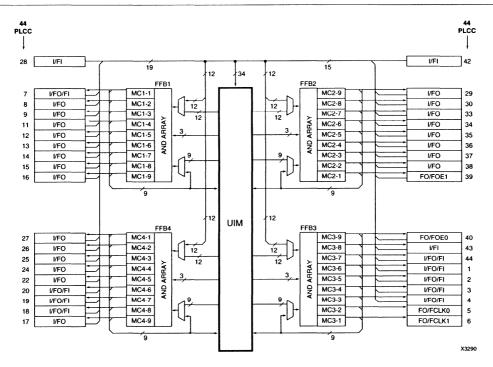

#### **Architectural Overview**

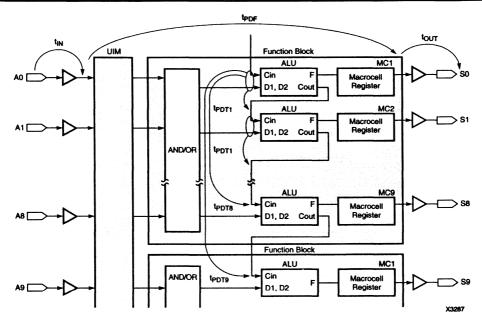

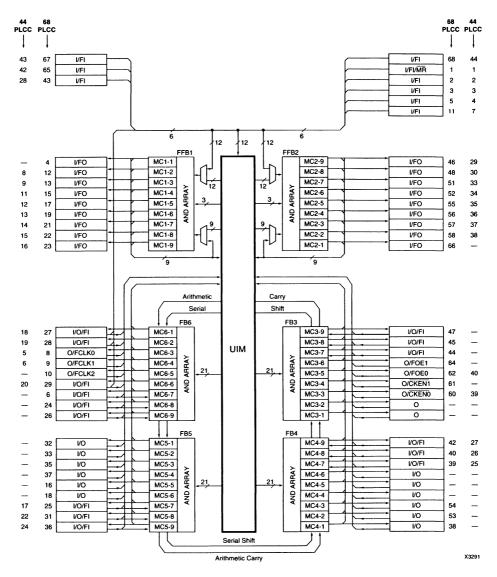

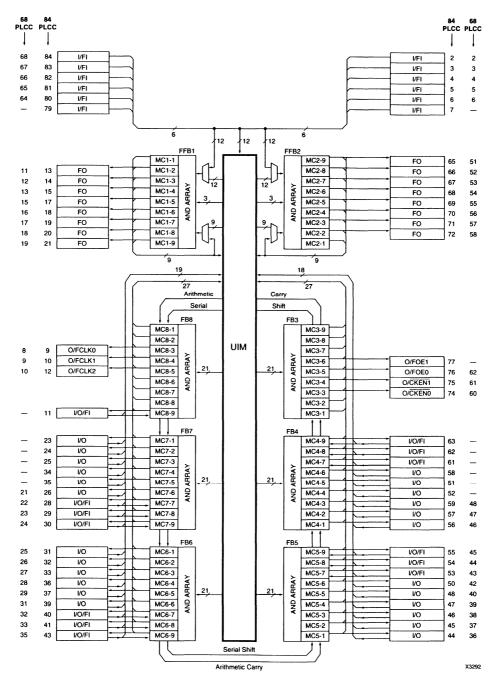

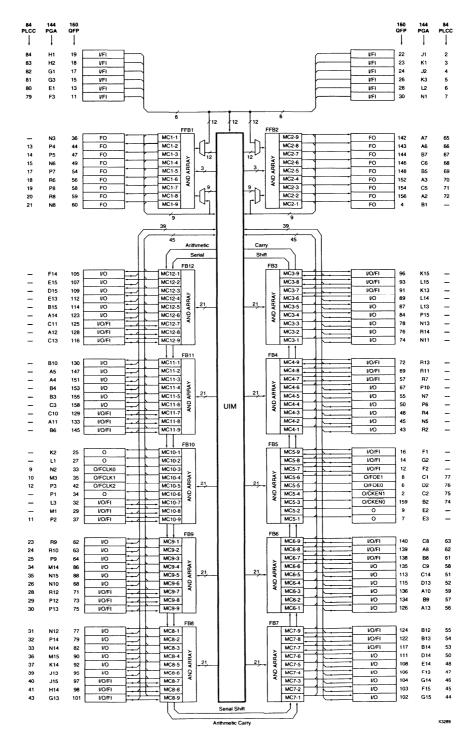

Figure 1 shows the XC7272A structure. Eight Function Blocks (FBs) are all interconnected by a central UIM. Each FB receives 21 signals from the UIM and each FB produces nine signals back into the UIM. All device inputs are also routed via the UIM to all FBs. Each FB contains nine output Macrocells that draw from a programmable AND array driven by the 21 signals from the UIM. Most Macrocells drive a 3-state chip output, all feed back into the UIM.

The device also contains two dedicated Fast Comparators (FCs) for address compare or decode functions. The following pages describe the elements of this architecture in detail.

Figure 1. XC7272A Architecture

#### **Function Blocks and Macrocells**

The XC7272A contains 72 Macrocells with identical structure, grouped into eight Function Blocks of nine Macrocells each. Each Macrocell is driven by product terms derived from the 21 inputs from the UIM into the Function Block.

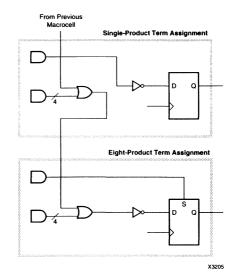

Five product terms are private to each Macrocell; an additional 12 product terms are shared among the nine Macrocells in any Function Block. One of the private product terms is a dedicated clock for the flip-flop in the Macrocell. See the description on page 3-24 for other clocking options.

The remaining four private product terms can be selectively ORed together with up to three of the shared product terms, and drive one input to an Arithmetic Logic Unit. The other input to the ALU is driven by the OR of up-to-nine product terms from the remaining shared product terms.

As a programmable option, two of the private product terms can be used for other purposes. One is the asynchronous active-High Reset of the Macrocell flip-flop, the other can be either an asynchronous active-High Set of the Macrocell flip-flop, or an Output-Enable signal.

The Arithmetic Logic Unit has two programmable modes: In the *logic mode*, it is a 2-input function generator, a 4-bit look-up table, that can be programmed to generate any Boolean function of its two inputs. It can OR them, widening the OR function to max 16 inputs; it can AND them, which means that one sum of products can be used to mask the other; it can XOR them, toggling the flip-flop or comparing the two sums of products. Either or both of the sum-of-product inputs to the ALU can be inverted, and either or both can be ignored. The ALU can implement one additional layer of logic without any speed penalty.

In the arithmetic mode, the ALU block can be programmed to generate the arithmetic sum or difference of two operands, combined with a carry signal coming from the lower Macrocell; it also feeds a carry output to the next higher Macrocell. This carry propagation chain crosses the boundaries between Function Blocks, but it can also be configured 0 or 1 when it enters a Function Block.

This dedicated carry chain overcomes the inherent speed and density problems of the traditional EPLD architecture, when trying to perform arithmetic functions like add, subtract, and magnitude compare.

Figure 2. Function Block and Macrocell Schematic Diagram

The ALU output drives the D input of the Macrocell flip-flop.

Each flip-flop has several programmable options:

One option is to eliminate the flip-flop by making it transparent, which makes the Q output identical with the D input, independent of the clock.

If this option is *not* programmed, the flip-flop operates in the conventional manner, triggered by the rising edge on its clock input.

The clock source is programmable: It is either the dedicated product term mentioned above, or it is one of the two global FastCLK signals that are distributed with short delay and minimal skew over the whole chip.

The asynchronous Set and Reset (Clear) inputs override the clocked operation. If both asynchronous inputs are active simultaneously, Reset overrides Set. Upon powerup, each Macrocell flip-flop can be preloaded with either 0 or 1.

In addition to driving the chip output buffer, the Macrocell output is also routed back as an input to the UIM. When the Output Enable product term mentioned above is not active, this feedback line is forced High and thus disabled.

#### **Universal Interconnect Matrix**

The UIM receives 126 inputs: 72 from the 72 Macrocells, 42 from bidirectional I/O pins, and 12 from dedicated input pins. Acting as an unrestricted crossbar switch, the UIM generates 168 output signals, 21 to each Function Block.

Any one of the 126 inputs can be programmed to be connected to any number of the 168 outputs. The delay through the array is constant, independent of the apparent routing distance, the fan-out, fan-in, or routing complexity. Routability is not an issue: Any UIM input can drive any UIM output, even multiple outputs, and the delay is constant.

When multiple inputs are programmed to be connected to the same output, this output becomes the AND of the input signals if the levels are interpreted as active High. By choosing the appropriate signal inversion in the Macrocell outputs and the Function Block AND-array input, this AND-logic can also be used to implement a NAND, OR, or NOR function, thus offering an additional level of logic without any speed penalty.

A Macrocell feedback signal that is disabled by the output enable product term represents a High input to the UIM. Several such Macrocell outputs programmed onto the same UIM output thus emulate a 3-state bus line. If one of

Figure 3. Input/Output Schematic Diagram

the Macrocell outputs is enabled, the UIM output assumes that same level.

#### **Outputs**

Sixty of the 72 Macrocells drive chip outputs directly through 3-state output buffers, each individually controlled by the Output Enable product term mentioned above. For bidirectional I/O pins, an additional programmable cell can optionally disable the output permanently. The buried flipflop is then still available for internal feedback, and the pin can still be used as a separate input

#### Inputs

Each signal input to the chip is programmable as either direct, latched, or registered in a flip-flop. Latch and flip-flop can be programmed with either of the two FastCLK signals as latch enable or clock. The latch is transparent when FastCLK is High, and the flip-flop clocks on the rising edge of FastCLK. Registered inputs allow high system clock rates by pipelining the inputs before they incur the

combinatorial delay in the device, in cases where a pipeline cycle is acceptable.

The direct, latched, or registered inputs then drive the UIM. There is no propagation-delay difference between pure inputs and I/O inputs.

#### **FastCompare**

Two 12-bit wide fast identity (equality) comparators are driven by the 12 dedicated FCI inputs, which also drive into the UIM. These dedicated circuits compare the input data against two sets of 12-bit data, either loaded previously from the same data inputs, or pre-programmed into the device.

As a programming option, any bit can be excluded from the comparison (disabled), the whole comparison can be disabled (forced false), and the polarity of the response can be chosen. The FCO comparator outputs can substitute the MC 5-1 and 5-2 outputs. Since this compare circuitry bypasses the UIM and the AND/OR logic, it is very fast and can also be used as a high-speed address decoder.

Figure 4. FastCompare Schematic Diagram

#### Programming and Using the XC7272A

The features and capabilities described above are used by the Xilinx development software to program the device according to the specification given either through schematic entry, or through a behavioral description expressed in Boolean equations.

The user can specify a security bit that prevents any reading of the programming bit map after the device has been programmed and verified.

The device is programmed in a manner similar to an EPROM (ultra-violet light erasable read-only memory) using the Intel Hex format. Programming support is available from a number of programmer manufacturers. The UIM connections and Function Block AND-array connections are made directly by non-volatile EPROM cells. Other control bits are read out of the EPROM array and stored into latches just after power-up. This method,

common among EPLD devices, requires either a very fast  $V_{CC}$  rise time (<5 µs) or the application of a master-reset signal delayed at least until  $V_{CC}$  has reached the required operating voltage. The latter can be achieved using a simple capacitor and pull-up resistor on the MR pin (the RC product should be larger than twice the  $V_{CC}$  rise time). The power-up or reset signal initiates a self-timed configuration period lasting about 350 µs ( $t_{RESET}$ ), during which all device outputs remain disabled and programmed preload state values are loaded into the macrocell registers.

Unused input and I/O pins should be tied to ground or Vcc or some valid logic level. This is common practice for all CMOS devices to avoid dissipating excess current through the input-pad circuitry.

The recommended decoupling capacitance on the three  $V_{CC}$  pins should total 1  $\mu F$  using high-speed (tantalum or ceramic) capacitors.

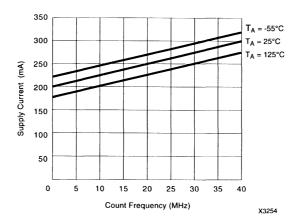

Typical Power Requirements for XC7272A Configured as Sixteen 4-bit Counters ( $V_{CC} = +5.0 \text{ V}$ ,  $V_{IN} = V_{CC}$  or GND, all outputs open)

## **Absolute Maximum Ratings**

|                  |                                                          |              | Units |

|------------------|----------------------------------------------------------|--------------|-------|

| V <sub>cc</sub>  | Supply voltage relative to GND                           | -0.5 to 7.0  | ٧     |

| V <sub>IN</sub>  | Input voltage with respect to GND                        | -0.5 to 7.0  | ٧     |

| V <sub>TS</sub>  | Voltage applied to 3-state output                        | -0.5 to 7.0  | ٧     |

| T <sub>STG</sub> | Storage temperature                                      | -65 to + 150 | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in. = 1.5 mm) | + 260        | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

### **Operating Conditions**

|                 |                                                                          | Min  | Max                   | Units |

|-----------------|--------------------------------------------------------------------------|------|-----------------------|-------|

| V <sub>cc</sub> | Supply voltage relative to GND Commercial t <sub>A</sub> = 0°C to 70°C   | 4.75 | 5.25                  | ٧     |

|                 | Supply voltage relative to GND Industrial t <sub>A</sub> = -40°C to 85°C | 4.5  | 5.5                   | ٧     |

|                 | Supply voltage relative to GND Military t <sub>C</sub> = -55°C to 125°C  | 4.5  | 5.5                   | ٧     |

| V <sub>IH</sub> | High-level input voltage                                                 | 2.0  | V <sub>cc</sub> + 0.3 | ٧     |